Čas v preklopnih vezjih

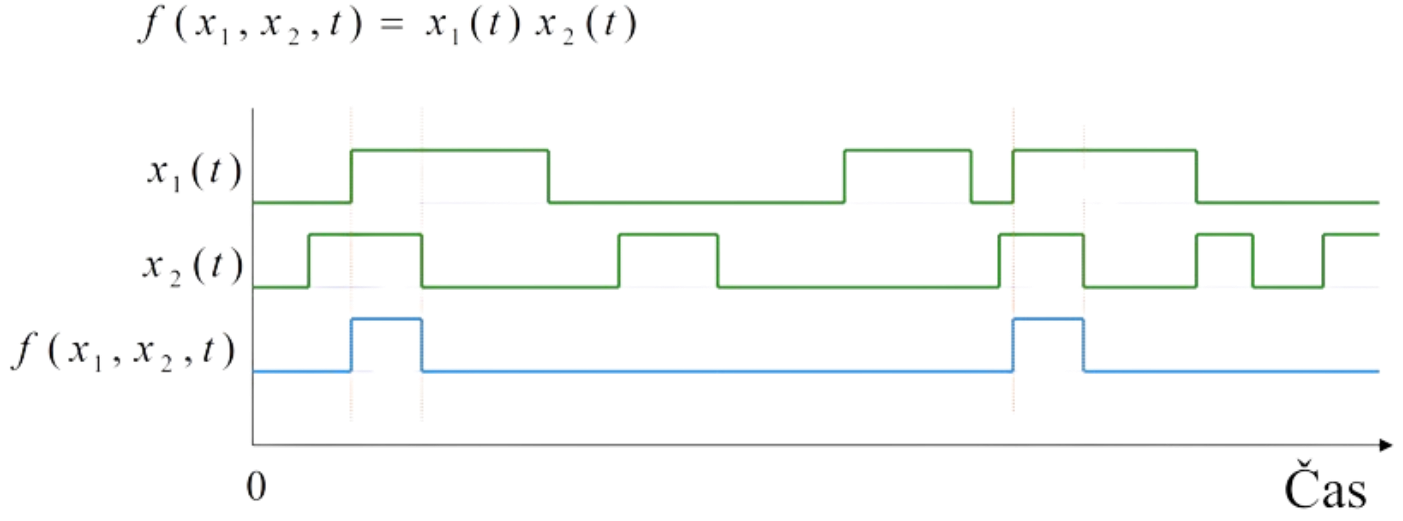

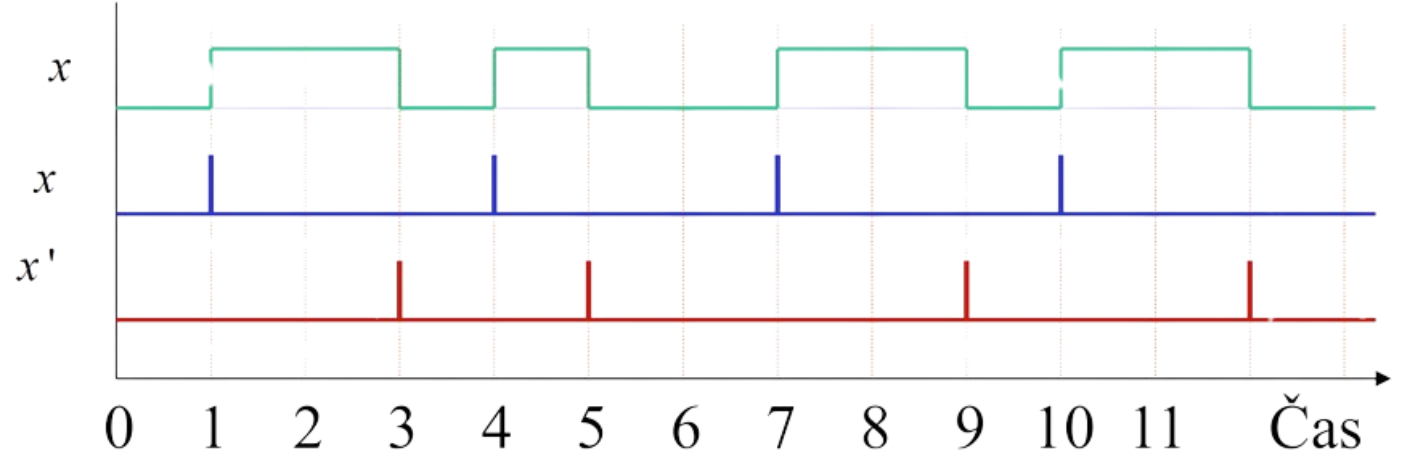

Spreminjanje vrednosti spremenljivk lahko opazujemo v času:

Časovni operator

Predstavlja premik vhodne spremenljivke v času za enot:

- … sedanjost

- … preteklost

- … prihodnost

Lastnosti:

- (velja za katerokoli funkcijo)

Fronta

Sprememba nivoja spremenljivke v času:

- Prva fronta : sprememba iz nizkega v visoko stanje (iz v )

- Zadnja fronta : sprememba iz visokega v nizko stanje (iz v )

Pomnilne celice

Pomnenje ~ ohranjanje stanja

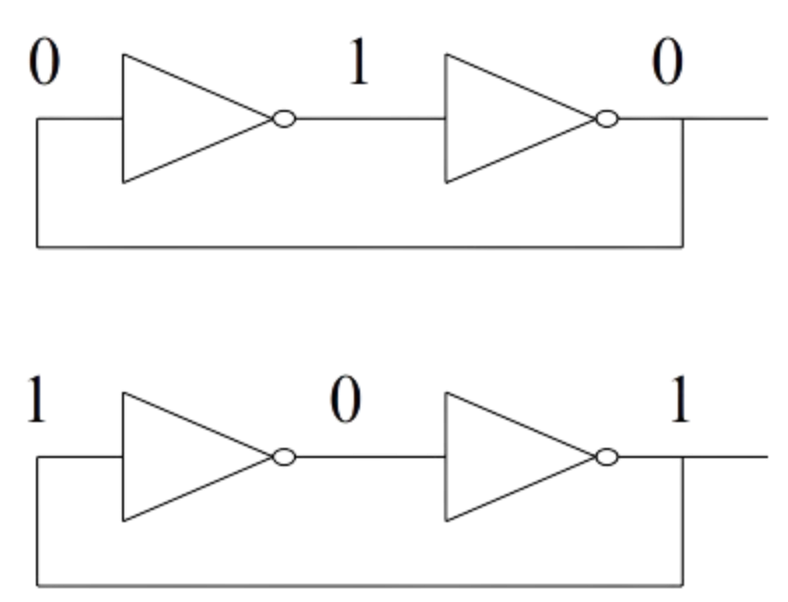

Bistabil

Vezje lahko zavzame obe stabilni stanji izhoda

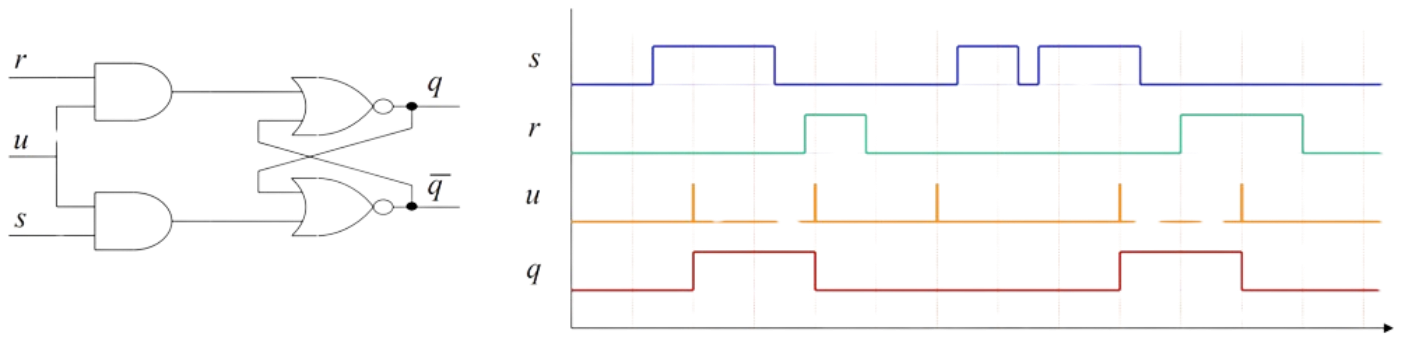

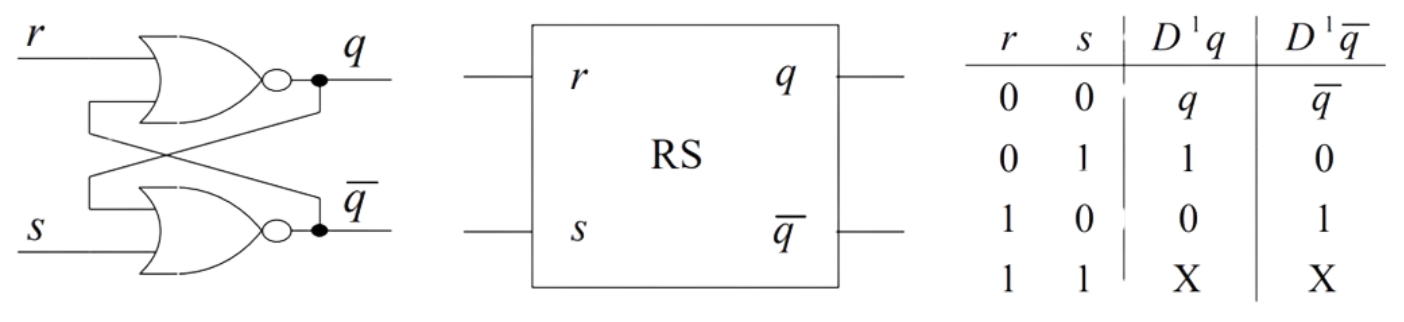

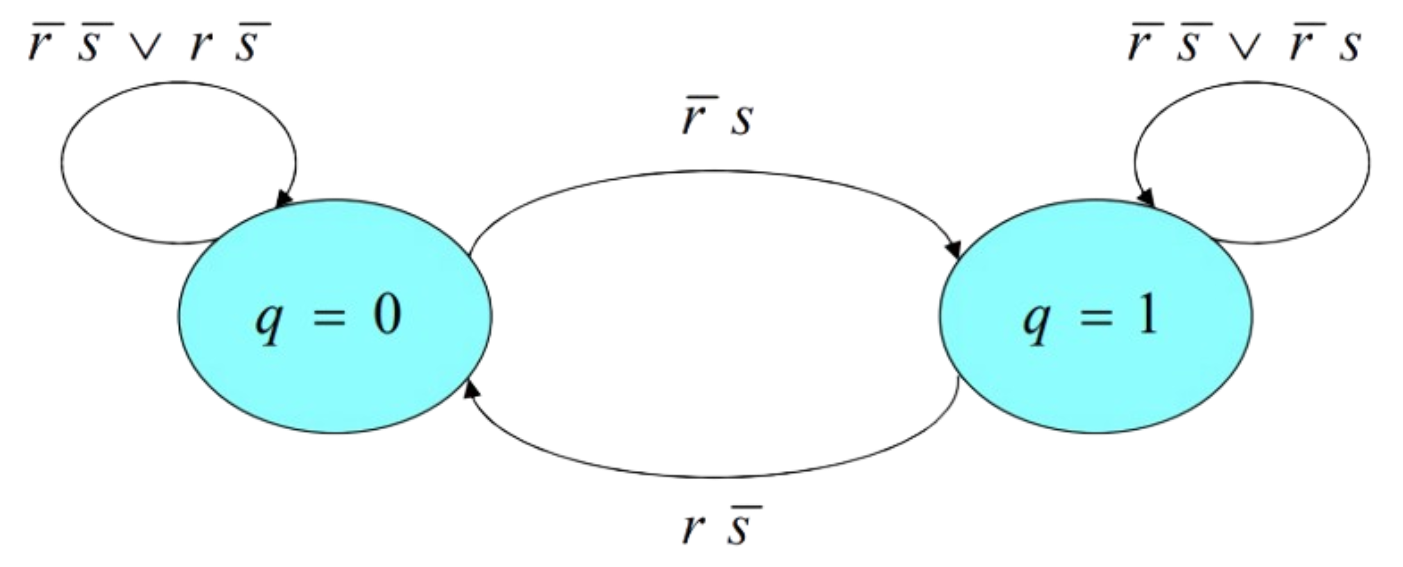

RS celica

Če razširimo bistabil dobmo Reset-Set pomnilno celico

Če sta oba vhoda (set in reset) na logični enici, dobimo nestabilno (nedoločeno) stanje.

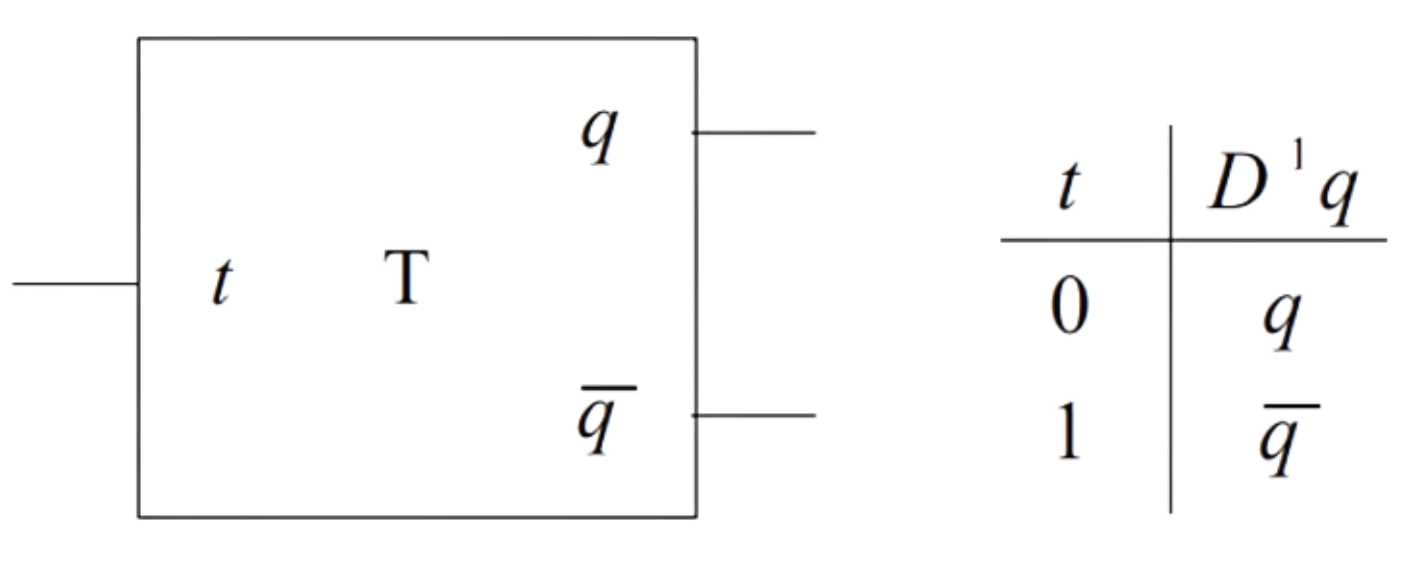

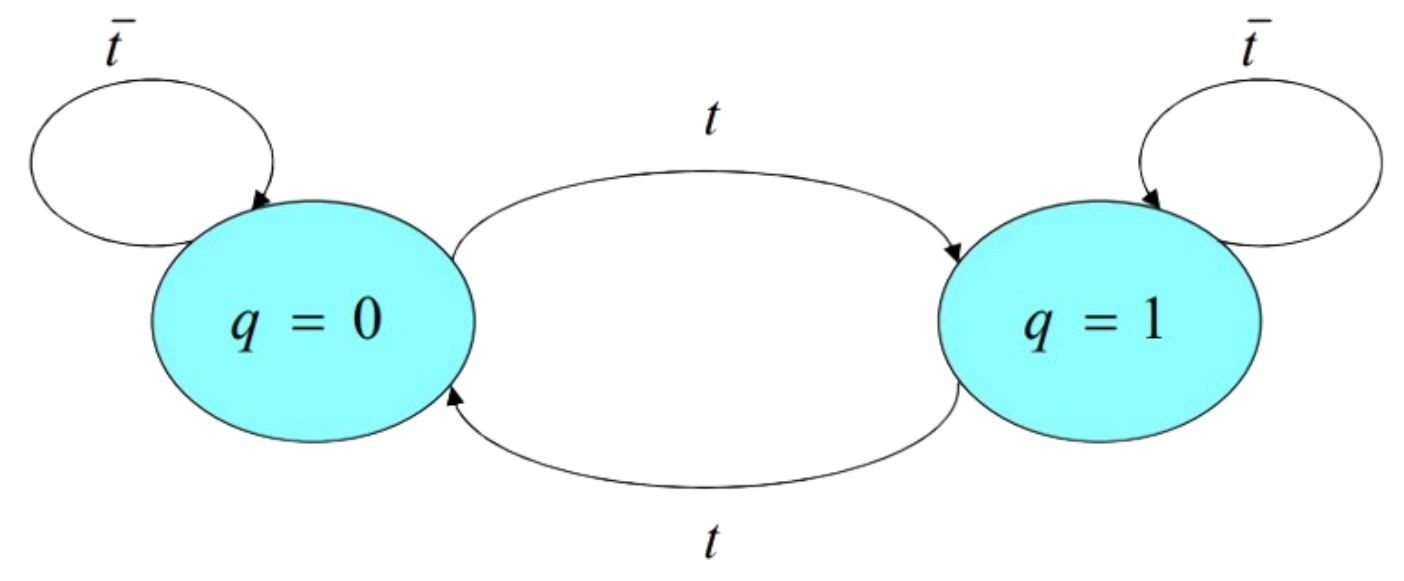

T pomnilna celica

Trigger pomnilna celica ima en vhod, katerega visoko stanje spremeni vrednost celice, pri nizkem stanju pa se ohranja

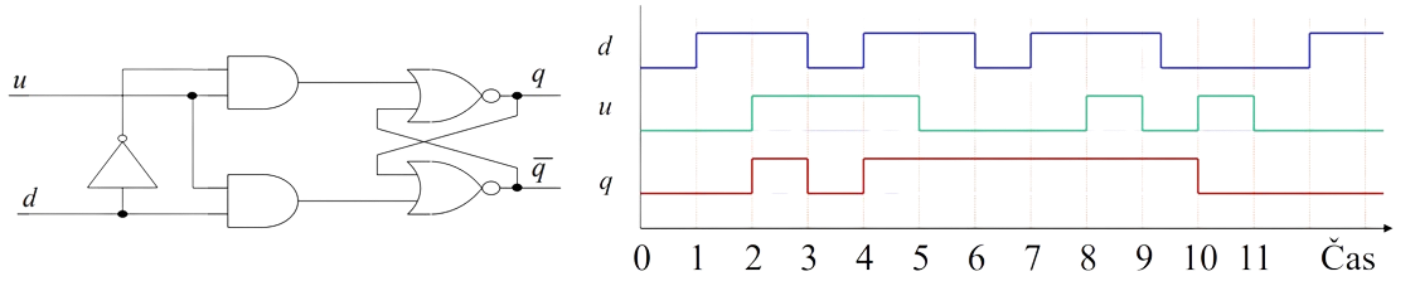

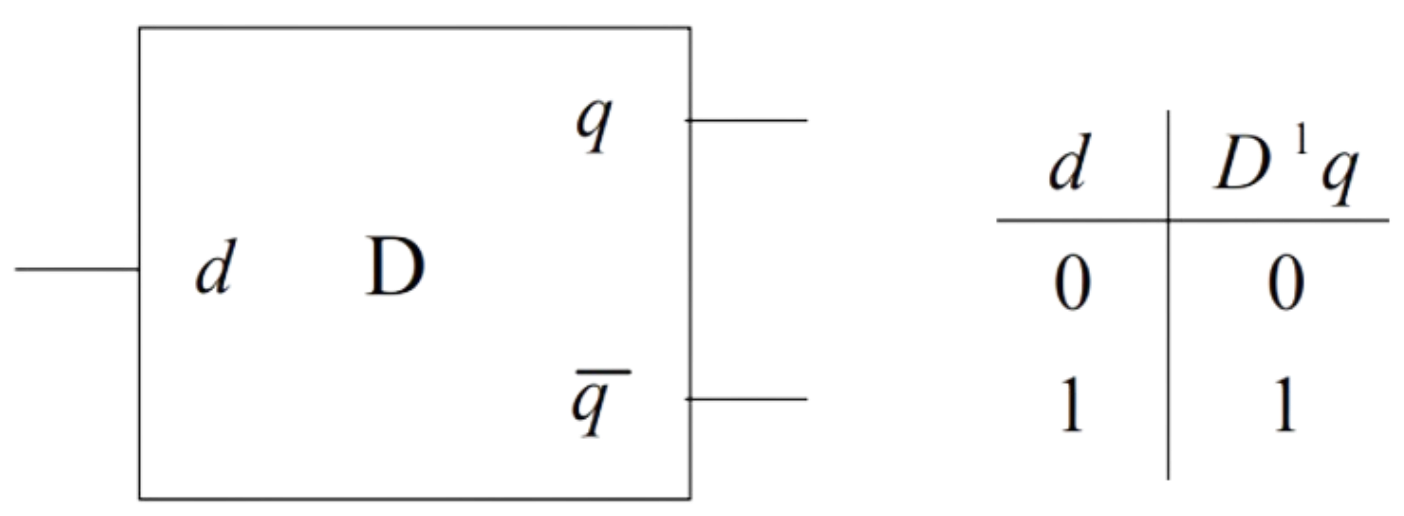

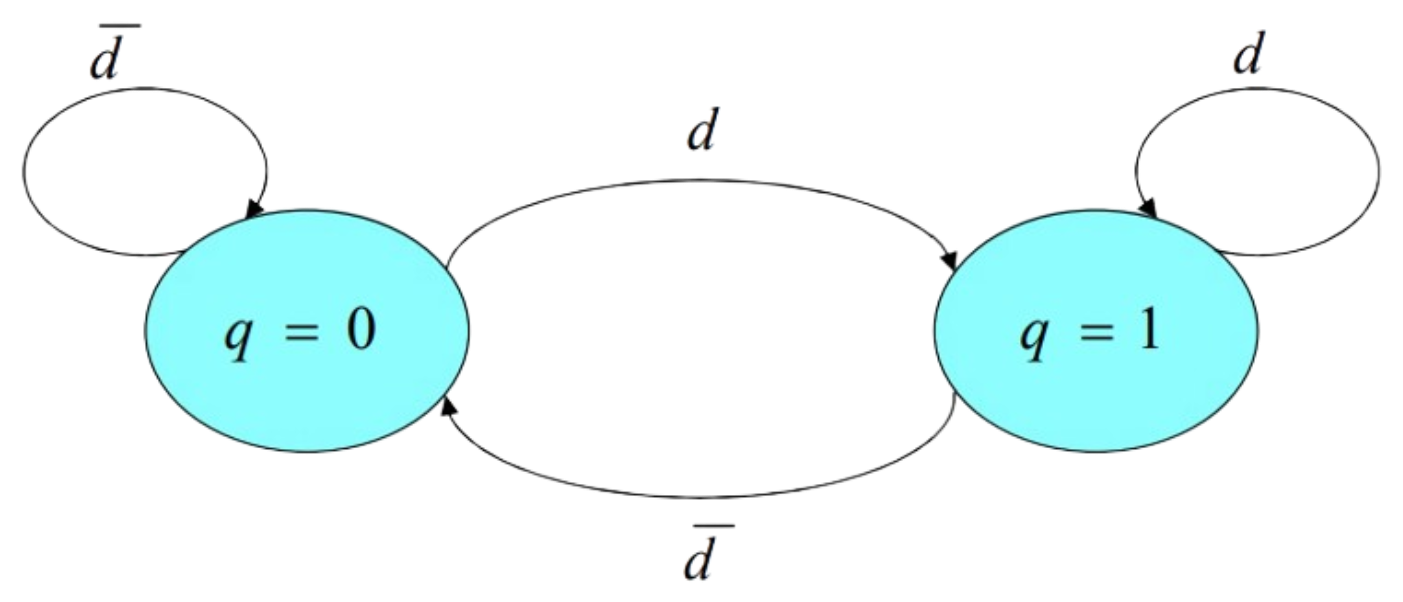

D pomnilna celica

Delay pomnilna celica ima en vhod; vrednost pomnilne celice je zakasnjena vrednost vhoda

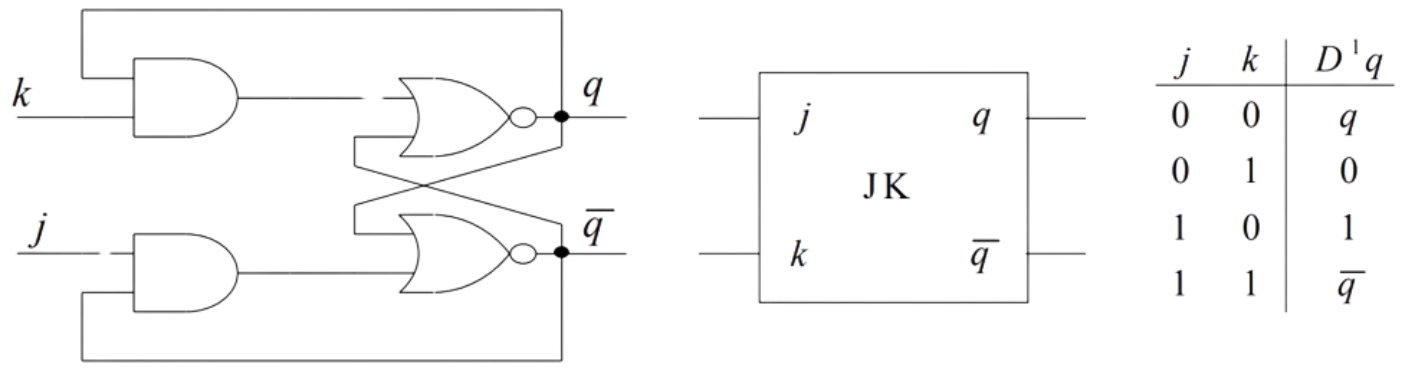

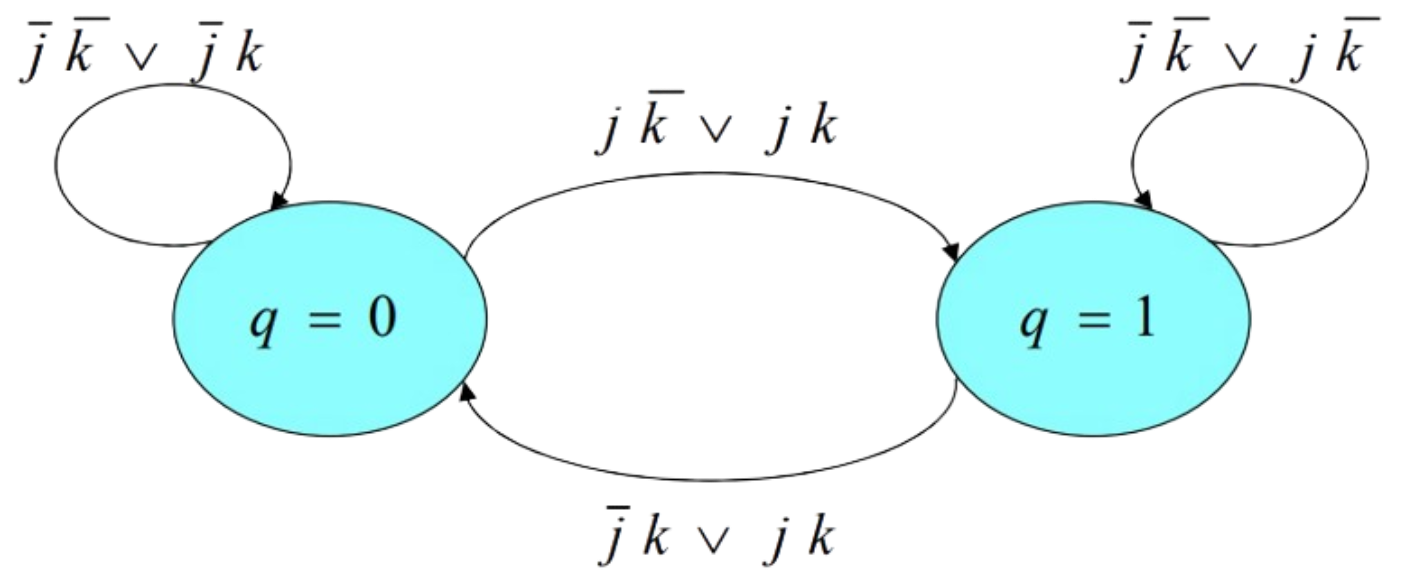

JK pomnilna celica

Jump-Kill pomnilna celica ima dva vhoda - brezpogojno nastavi vrednost celice, jo brezpogojno ponastavi, v primeru visoke vrednosti obeh vhodov pa se vrednost celice negira

Sinhrone pomnilne celice

Pri T in JK pomnilni celici je problem proženja vhodov, ki negirajo vrednost - uvedemo sinhronizacijo na urin impulz (izredno kratko trajanje visoke vrednosti)

Sinhroni RS in D pomnilni celici

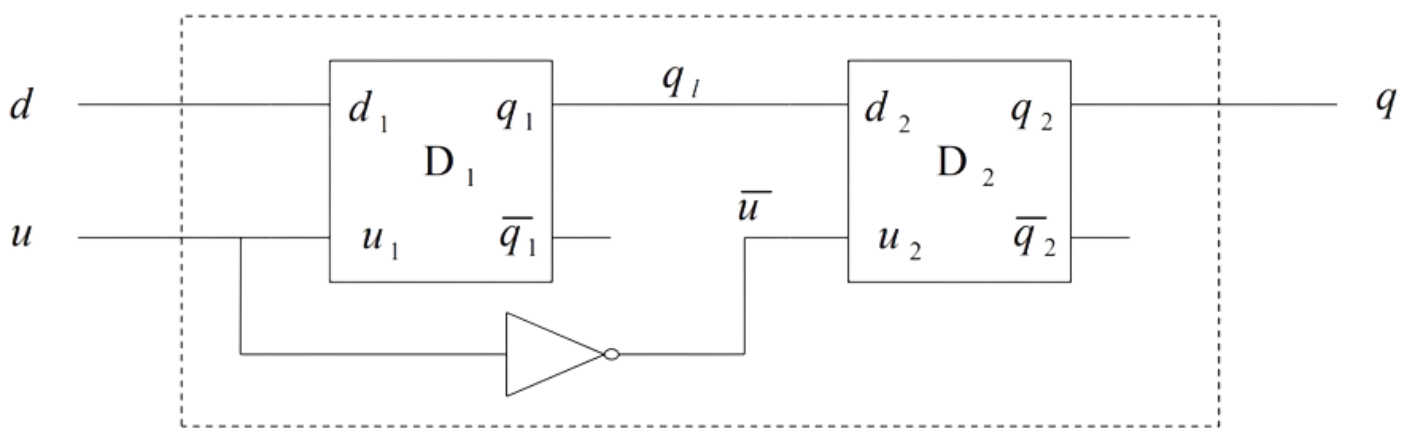

Pomnilne celice s predpomnenjem

Dobimo jih z zaporedno vezavo več pomnilnih celic

- Prva pomnilna celica spreminja svojo vrednost ob visokim urinem impulzu

- Druga pomnilna celica spreminja svojo vrednost ob nizkem urinem impulzu

- Do spremembe pride samo pri prehodu iz visokega v nizko stanje - zadnji urini fronti

D pomnilna celica s predpomnenjem

Paralelno zajemanje podatkov

Ponavadi pomnilne celice vežemo skupaj - hranjenje več bitov hkrati, vezano na en urin signal

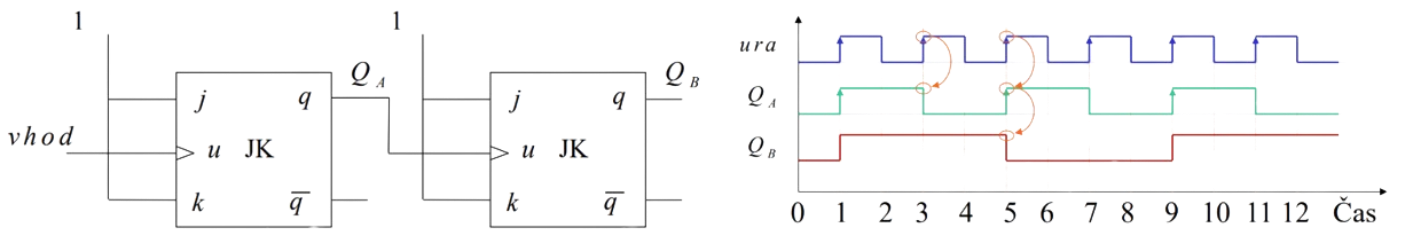

Delilnik frekvence

Z JK celico lahko zgradimo delilnih frekvence:

Števec

Z JK celico lahko zgradimo števec - sestavljene vrednosti pomnilnih celic skozi čas predstavljajo dvojiško štetje

Taka izvedba ni najboljša, saj moramo zaradi zamika čakati period ure za pravilno nastavitev

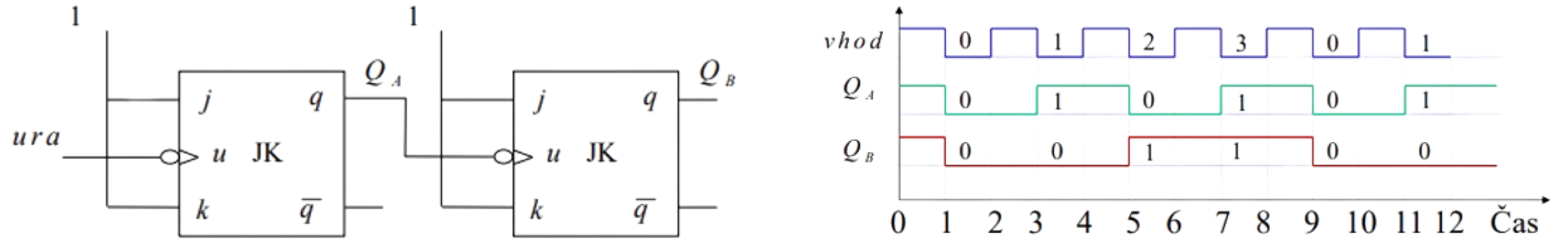

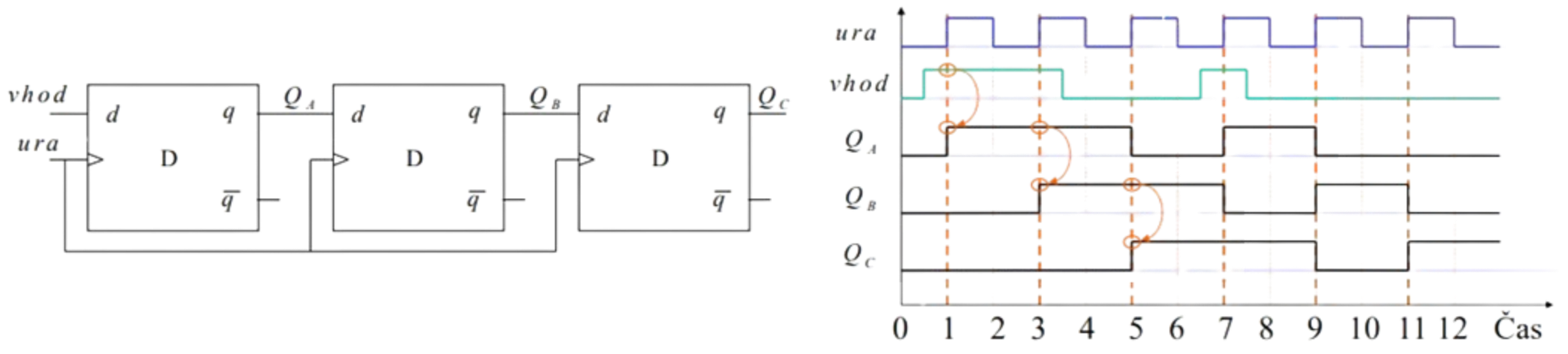

Pomikalni register

Z D pomnilno celico zgradimo pomikalni register - začetno stanje pomnilnih celic se krožno premika

Model sekvenčnega vezja

Splošen model:

- … vektor vhodnih spremenljivk

- … vektor izhodnih spremenljivk

- … vektor krmilnih spremenljivk

- … vektor izhodov iz pomnilnih celic

SInhronizacija je izvedena z uro, ki vstopa v PC (pomnilne celice)