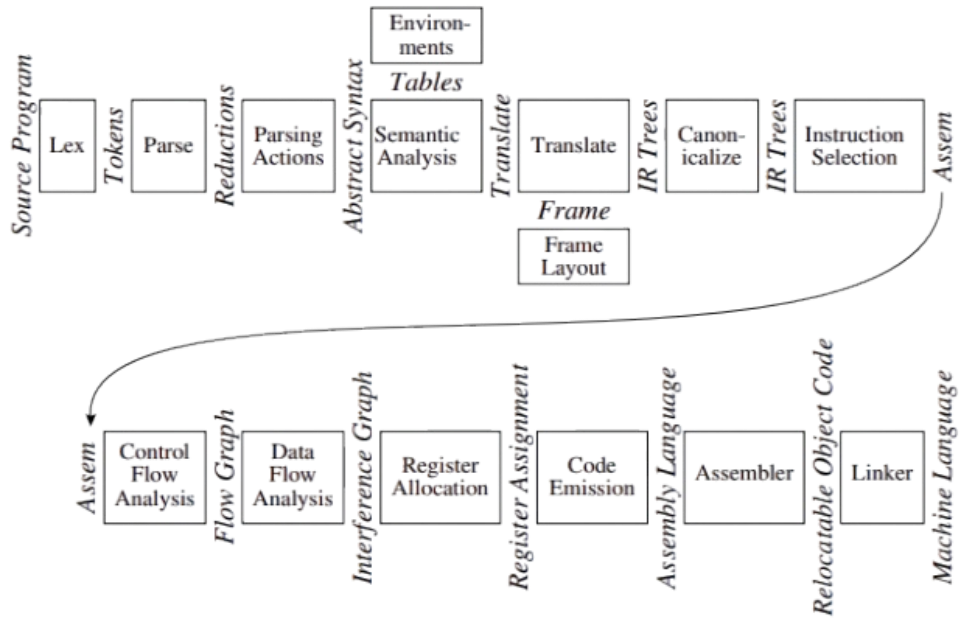

Princip cevovoda:

- vhod: izvorna koda (npr. C/Go/Pascal/…)

- izhod: ciljna koda zbirnika za specifičen procesor (npr. Intel/AMD/RISC-V/…)

Faze zbiranja:

- Leksikalna analiza: zaporedje znakov vhodne datoteke razbijemo v zaporedje leksikalnih simbolov

- Sintaksna analiza: po preverjanju zaporedja/strukture leksikalnih simbolov zgradi drevo izpeljav

- Abstraktna sintaksa: poenostavitev drevesa izpeljav v abstraktno sintaksno drevo

- Semantična analiza: pregled pomena simbolov, povezava uporabe spremenljivk z njihovimi definicijami, preverjanje tipov izrazov, …

- Izračun klicnih zapisov: postavitev spremenljivk, parametrov v pomnilnik - sklad ali izven sklada (odvisno od ciljne arhitekture)

- Generacija vmesne kode: vmesna koda podobna kot strojna koda, a na višjem nivoju

- Osnovni bloki: linearizacija vmesne kode, že poganjljiva v tolmaču

- Generacija strojne kode: generacija ukazov za konkreten procesor, brez konkretnih registrov (kot da imamo poljubno št. registrov)

- Analiza registrov: zbiranje informacij o aktivnosti spremenljivk - registrov

- Dodeljevanje registrov: dodeljevanje registrov spremenljivkam in drugim vrednostim

- Izpis ciljne kode: ustvarjanje datotek, za funkcije potrebne oznake za povezovalnik, …

- (Zbirnik in povezovalnik)

Sprednji del prevajalnika (1-6): izvorni jezik (znaki drevesa ) vmesna koda

(Vmesni del: optimizacije vmesne kode)

Zadnji del prevajalnika(6-11): vmesna koda ciljni jezik

Modularnost omogoča spremembo/dodajanje:

- ciljne arhitekture popravi/dodaj fazi Izračun klicnih zapisov ter Generacija strojne kode

- izvornega jezika - popravi/dodaj vse faze do generacije vmesne kode